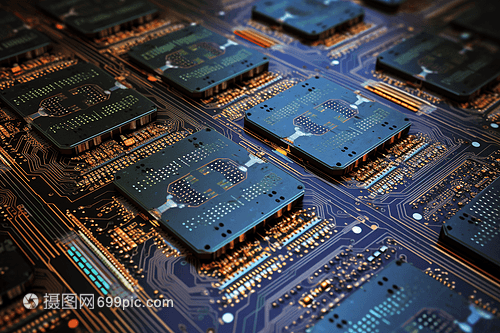

互联互通 微芯片概念图中的集成电路设计智慧

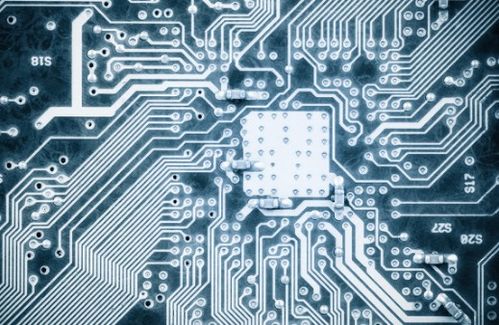

在信息时代的浪潮中,微芯片作为现代电子设备的核心,其设计理念与实现方式深刻影响着科技发展的轨迹。而“相互连接的微芯片概念图”这一图像,不仅是技术蓝图的视觉呈现,更是一扇窥探集成电路(IC)设计复杂性与艺术性的窗口。它直观地揭示了芯片内部及芯片之间如何通过精密的互连结构,协同工作以执行庞杂的计算任务。

概念图:从抽象到具体的桥梁

一张典型的相互连接微芯片概念图,往往超越了单一芯片的边界,描绘了多个功能模块(或称“芯粒”Chiplet)通过先进封装技术(如2.5D/3D IC、硅中介层、扇出型封装等)集成在一起的场景。图中,不同颜色或形状的区域代表不同的功能单元——可能是中央处理器(CPU)核心、图形处理器(GPU)单元、内存块、高速输入输出(I/O)接口或专用人工智能(AI)加速器。连接这些单元的,是密密麻麻、多层交织的“连线”网络,象征着数据通路、控制信号和电源分配网络。

这幅图的核心价值在于将高度抽象的电路网表、物理布局和时序约束,转化为一种更易为跨学科团队(包括架构师、设计师、验证工程师甚至市场人员)理解的视觉语言。它强调了“连接”本身的重要性:不仅是晶体管之间的连接,更是模块间、芯片间乃至系统级的连接。

集成电路设计:连接背后的精密工程

概念图所描绘的美好愿景,需通过极其严谨的集成电路设计流程来实现。这个过程可以概括为几个关键阶段,而“互连”是贯穿始终的主题:

- 系统架构与划分:设计师首先确定整体功能,并将其划分为可独立设计、制造的模块或芯粒。概念图在此阶段萌芽,用于评估模块间通信带宽、延迟和功耗需求。

- 逻辑与电路设计:使用硬件描述语言(HDL)定义每个模块的功能。此时,“连接”表现为模块端口之间的信号定义。

- 物理设计:这是将逻辑转化为实际几何版图的核心。包括:

- 布局规划:确定每个功能模块在芯片上的大致位置,类似于概念图中的区域划分,目标是优化互连长度,减少信号延迟和功耗。

- 布线与互连:这是实现“相互连接”最直接的步骤。现代芯片拥有多达十几层的金属连线层,通过计算机辅助设计(CAD)工具进行全局和详细布线,在满足电气规则(如宽度、间距、寄生参数)的前提下,连接起数百万乃至数十亿个节点。电源网格网络也在此精心布设,为整个芯片提供稳定能量。

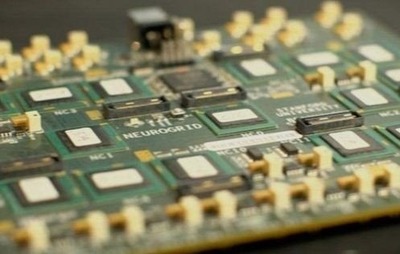

- 封装与系统集成:对于多芯片模块,设计重点转向了芯片间的互连技术。概念图中芯片间的那些粗大“通道”,对应着硅通孔(TSV)、微凸块、再分布层(RDL)等先进互连结构,它们负责在极短距离内实现高带宽、低功耗的芯片间通信,是突破单芯片性能与制造瓶颈的关键。

挑战与未来趋势

相互连接的微芯片概念图也清晰地映射出当前IC设计面临的严峻挑战:

- 互连延迟与功耗:随着工艺节点微缩,晶体管开关速度加快,但金属连线的延迟和功耗问题却日益突出,成为性能提升的主要瓶颈。

- 信号完整性:密集的互连容易产生串扰、噪声和电磁干扰,设计时必须进行精细的建模与仿真。

- 热管理:高度集成的互联结构会导致热量积聚,有效的散热设计至关重要。

- 设计复杂性:连接规模的爆炸式增长使得设计验证和物理实现的难度呈指数级上升。

概念图将继续演进,指向更前沿的设计范式:

- 芯粒与异构集成:像搭积木一样组合不同工艺、功能的芯粒,通过先进互连构成“超级芯片”,是延续摩尔定律的主流方向。概念图将更侧重于系统级封装(SiP)的互连架构。

- 光互连:在芯片内部或芯片间引入光通信链路,以应对电互连在带宽和能耗上的极限。未来的概念图中或许会出现“光波导”与“电子线路”共存的景象。

- 三维集成:通过堆叠晶体管层或芯片层,在垂直维度上实现更短、更密集的连接,极大提升集成密度和能效。

- AI赋能设计:机器学习技术正被用于自动优化布局布线,探索人类设计师难以企及的复杂互连方案,自动生成更优的概念蓝图。

###

一张“相互连接的微芯片概念图”,远不止是一幅技术插图。它是集成电路设计哲学的浓缩,彰显了在纳米尺度上构建智能世界的核心逻辑——通过极致的、层次化的“连接”,将简单的物理结构编织成复杂的计算系统。随着互连技术从芯片内走向芯片间,再走向光电融合与三维空间,这张概念图所承载的想象力与工程实践,将继续驱动着计算技术向更强大、更高效、更智能的未来迈进。它提醒我们,在数字世界的底层,一切都是关于如何更好地建立与维护那些看不见的桥梁与脉络。

如若转载,请注明出处:http://www.58xiaolin.com/product/51.html

更新时间:2026-02-27 07:25:28