095期集成电路设计精选科技成果推荐

随着全球数字化转型加速,集成电路(IC)作为信息产业的核心基石,其设计技术的创新与发展备受瞩目。本期聚焦集成电路设计领域,精选了数项具有前瞻性与应用潜力的科技成果,旨在为产业界和学术界提供参考与启发。

1. 超低功耗人工智能边缘计算芯片设计

该项成果针对物联网终端设备的严苛功耗限制,提出了一种基于稀疏化神经网络与动态电压频率调整(DVFS)的芯片架构。通过算法与硬件的协同优化,在主流视觉识别任务中,其能效比达到15 TOPS/W,相比传统设计提升约3倍,同时保持了高识别精度。该芯片可广泛应用于智能安防、可穿戴设备及工业传感节点,显著延长设备续航时间。

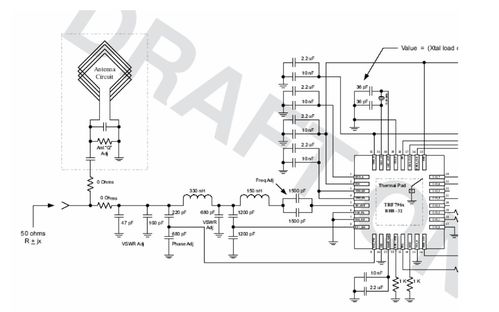

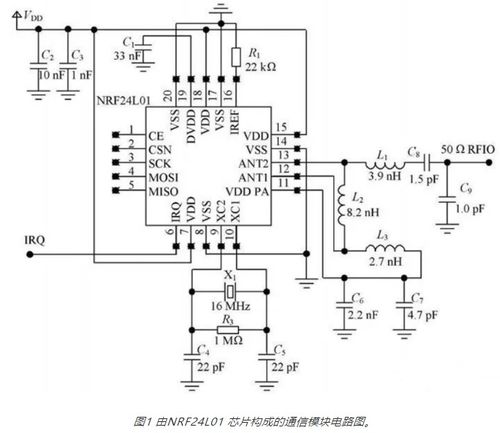

2. 面向5G/6G通信的高性能射频前端集成方案

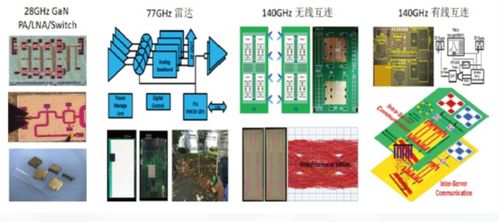

本技术攻克了高频、高线性度与高集成度难以兼得的难题,采用新型硅基化合物半导体异质集成工艺,将功率放大器(PA)、低噪声放大器(LNA)及开关等模块 monolithic 集成。实测显示,在28GHz频段下,其输出功率达到27dBm,效率超过40%,同时噪声系数低于3dB。该方案为下一代通信设备的小型化与高性能化提供了关键支持。

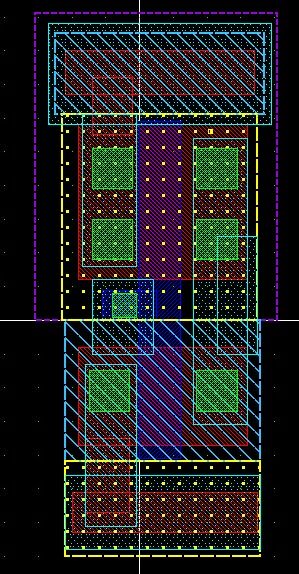

3. 基于存算一体架构的深度学习加速器

突破传统冯·诺依曼架构的“内存墙”瓶颈,该设计利用电阻式存储器(ReRAM)实现模拟域乘加运算,将数据存储与处理在物理层面融合。测试芯片在ResNet-50网络推理中,相比同工艺GPU,能效提升达两个数量级,延迟降低90%。该技术特别适合数据中心、自动驾驶等对实时性与能效要求极高的场景。

4. 汽车电子功能安全芯片设计平台

遵循ISO 26262 ASIL-D最高安全等级标准,该平台提供了从架构、设计、验证到故障注入测试的全套工具链与方法学。其核心包括锁步双核处理器、安全监控单元及错误纠正码(ECC)内存控制器,可系统性检测并缓解随机硬件故障。已成功应用于多款国产智能驾驶控制器芯片,助力提升汽车电子系统的可靠性。

5. 开源高性能RISC-V处理器核及生态工具

该项目推出了一款主频可达2GHz的64位多核RISC-V处理器IP,采用12nm工艺实现,并配套提供完整的软件开发套件(SDK)与验证环境。其微架构支持乱序执行与矢量扩展,性能对标国际主流中高端内核。该开源项目降低了芯片设计门槛,为国内IC设计企业提供了自主可控的处理器基础选择,促进产业生态繁荣。

与展望

本期推荐的科技成果涵盖了人工智能、通信、计算架构、汽车电子及处理器生态等集成电路设计的关键方向,体现了向“更低功耗、更高性能、更强智能、更安全可靠”持续演进的技术趋势。这些成果不仅具有扎实的理论创新,更展现出明确的产业化应用前景。随着工艺演进与系统需求复杂化,跨学科协同、软硬件协同与开放生态建设,将成为推动集成电路设计突破的核心动力。

如若转载,请注明出处:http://www.58xiaolin.com/product/71.html

更新时间:2026-02-25 18:48:05